同步操作将从 浪潮RISC-V研究小组/RVWeekly 强制同步,此操作会覆盖自 Fork 仓库以来所做的任何修改,且无法恢复!!!

确定后同步将在后台操作,完成时将刷新页面,请耐心等待。

RV与芯片评论.20210403:2021年第14周(总第36期).md

http://training.eeworld.com.cn/course/6013

本课程是信息与电子工程及相关计算机专业的专业基础课,课程包括处理器RISC-V指令集、寻址模式、数据类型、汇编语言,处理器微结构、控制器和流水线,存储系统、高速缓存、虚拟存储,多处理器和并行技术,系统设计性能评估及软硬件协同设计方法等。

面向于计算机体系结构与集成电路设计领域,负责完成国家自然科学基金2项,国家“863”项目3项,霍英东教育基金优选课题、国家重点实验室基金5项等纵向项目,授权发明专利30余项,近期科研成果主要发表于IEEE Transactions on Computers, TVLSI, TACO等国际期刊。2003年主持设计了国内首款RISC/DSP媒体数字信号处理器(“浙大数芯”),负责设计具有自主知识产权的微处理器CPU IP核,该CPU IP核授权合作单位杭州士兰微电子股份有限公司面向消费类的音频系统芯片,截止2018年底销售系统芯片超过1360万颗,产生较好的经济效益和社会效益。

本课程是信息与电子工程及相关计算机专业的专业基础课,课程包括处理器RISC-V指令集、寻址模式、数据类型、汇编语言,处理器微结构、控制器和流水线,存储系统、高速缓存、虚拟存储,多处理器和并行技术,系统设计性能评估及软硬件协同设计方法等。

本课程可以和线下教学进行结合,为学生提供复习、答疑和自我评价的线上平台,进一步对课堂上所学内容进行巩固和拓展,加强学生和教师之间在课堂以外的交流;也作为高等院校信息工程和计算机相关专业的本科生学习“计算机组成与设计”、“计算机系统结构”等课程的在线学习资源;并可供与计算机相关的专业人士和高校的相关任课教师学习参考。

本课程基于RISC-V指令集架构进行解读教学,在掌握传统的计算机组成知识的同时,也能学习了解指令集与系统架构设计方法。

同学们,我们可以回顾一下 RISC-5 数据通路的设计过程,我们设计数据通路能在一个使用周期内完成一条 RISC-5 指令的执行,但在某条指令执行的时候,并不是所有的硬件单元都会用到。我们将指令执行过程划分为:取值,译码,执行,访存,写回 五个阶段。五个阶段是所有指令都要经历的,也有的阶段只有部分指令才会用到,我们在构建数据通路的过程中,通过认识了控制器的作用,控制器通过产生各种控制信号,控制着指令如何被执行,本节课就上到这里,谢谢大家。

Pipelined processor design (重点我们关注)处理器的流水线设计

流水线冒险: 流水线有这样一种情况,“在下一个时钟节拍中,下一条指令不能执行” 的这种情况,我们称为冒险或者痛苦,流水线中存在三种类型的冒险:

- 第一种叫结构冒险,指某个硬件资源,同时被多条指令请求使用,

- 第二种是数据冒险指定的数据依赖性,某条指令读写操作需要等待前一条指令执行完成,

- 第三种是控制冒险,指程序执行流向需要依赖于前一条指令的执行结果,

下面我们对这三种冒险进行详细的讲解, 首先是结构冒险 。

问题来源 :流水线中两个或更多的指令在同时向同一个硬件资源发出访问请求,

有两种方法可以解决结构冒险问题:

- 第一种是指定轮流使用这项资源,但有时有的指令可能不得不被阻塞,以等待空闲资源,

- 第二种是增加更多的硬件资源,以满足硬件需求结构冒险的问题

永远都是可以用增加硬件的方式来解决的。这种结构冒险可能发生在寄存器文件,因为在有些指令的译码阶段,可能需要读两个寄存器值,同时可能另一条指令刚好执行到写回阶段,需要写寄存器,这个时候寄存器文件需要同时处理两个读操作。和一个写操作,为了避免这种结构冒险,就要使用独立的端口,两个读端口和一个写端口,这样三个访问请求就能同时满足。

结构冒险,也有可能发生在存储器,比如在执行如图所示的指令优势,我们看到其中的 StoreWord 指令会在访存阶段,访问数据存储器保存的数据,而在它之后,第三条指令也会在同时进入取指阶段,访问指令存储器读取指令,这就是出现的指令存储器和数据存储器被同时使用的问题,我们通过两个分离的存储单元来解决该冒险。这节课就上到这里,谢谢大家。

在这一讲中,我们对流水线进行了更为深入的学习,流水线通过重叠多条指令的执行来提高吞吐率,在流水线中,所有流水席的持续时间都是相同的,已使用节拍时间一致,同时我们介绍了流水线中可能存在的冒险问题,这些冒险问题在一定程度上阻碍了处理器的性能的发挥。我们介绍了结构冒险和数据冒险,我们看到,虽然我们可以在处理器中采用一些避免这些冒险的结构机制设计,但并不能完全做到规避冒险的发生,想要使性能最大化,还是需要借助程序员和编译器的帮助,同学们本讲到此,谢谢大家。

最后我们简单介绍了超标量处理器的基本概念,超标量处理器采用多个执行单元实现指令级并行,提升处理器的性能,同学们本讲到此结束。

Caches (重点讲解)高速缓存cache的基本原理和设计

如何通过系统软件及操作系统来进行管理虚拟存储器

http://training.eeworld.com.cn/video/29472#showbbs

http://training.eeworld.com.cn/video/29439

我们使用的课本如右图所示是机械工业出版社2019年引进的计算机组成与设计为四和五版本。

其中高速缓存存储器cache是存储器的一种,中央处理器,包括执行单元功能单元cache功能单元。

在多个计算机上并行执行线程级并行,在多个处理器合格并执行指令级并行,通过同一时刻发射多条指令,利用多个功能单元,同时执行发射多条指令数据级并行,同一时刻对不同的数据做相同的运算操作,同时可以通过。硬件描述语言来描述硬件逻辑单元的并行,这也是硬件语言的特点之一一般来说,与软件开发最相关的是数据级并行指令级并行线程级并行任务级并行。

他预测,集中电路上可容纳的晶体管数目约每隔两年便会增加一倍,经常被赢的18个月是我英特尔首席执行官大卫豪斯提出的,预计18个月会将新的性能提高一倍及更多的晶体管,使其更快,是一种以倍数增长的观测摩尔定律,从目前来看一直有效。

从下图。我们可以看到密度也是考察特性之一,这个图来自于台积电TSMC在2019年后tips的专题演讲。

采用局部性原理来设计处理器,存储器层次离处理器最近的这种单元分别是寄存器cache物理存储固态存储器虚拟存储器等。这个存储器层次,我们在后面的讲解中会分别详细介绍。

指令级并行

和线程级并行等,

阿姆达尔定律,与阿姆的love是一个计算机科学界的经验法则,因吉恩阿姆达尔德里,它代表着处理器并行运算之后。效率提升的能力并行计算中的加速使用定型前的执行速度和定型后的执行速度之比来表示的,他表示了在定型化之后的效率提升情况,阿姆达尔定律是固定复杂的量化标准,该定理是指系统中某一部件采用更快执行方式所能。进程度取决于这种执行方式被使用的频率或所占总执行时间的比例。

我们可以看到,通过荣誉模块设计,实现可靠性的例子是用于从数据中心到存储器。到内存的所有设计中,例如通过数据中心的荣誉设计保证互联网络服务正常,谷歌公司提出的荣誉计算机的设计思路,独立磁盘冗余阵列的设计以及荣誉存储系统的设备设计等,

如何在晶体结构的研究工作呢,我们从图中可以观察到。目前,业界先进的cpu速度基本上维持在5G赫兹左右,但是经济管的提升度还在逐步提高,对设计功耗都有约束。

体系架构,随着应用和工艺技术也在不断的引进应用需求驱动技术的改进,改进的技术使应用成为现实,可能耳机应用性的软件开发成为目前。

未来的应用需要不可估量的计算能力,如高性能计算机器智能大数据分析等应用。

本讲我们介绍了计算机系统的表示,课程的主要内容及应用需求和体系架构,软件系统设计研究的必要性,本节课上到这里谢谢各位同学。

同学们好,本讲介绍,计算机组成与设计mooc课程的基本内容构成这门课的预修课程要求主要包括以下几门课程,第一是数字系统设计或者数字电路设计课程,第二是C语言或者python语言的学习,第三是对硬件电路描述语言v log,另外如果同学们学习的。编译原理操作系统和集中电路设计等课程对计算机组成与设计的这门课学习会很有帮助,我们使用的课本如右图所示是机械工业出版社2019年引进的计算机组成与设计为四和五版本。

本门课的主题主要包括,一软硬件接口机器语言和汇编语言的编程,二编译器的优化和性能评估方法,三处理器设计重点,我们关注处理器的流水线设计,四存储器层次设计,重点讲解高速缓存cache的基本原理和设计。五虚拟存储器如何通过系统软件及操作系统来进行管理,虚拟存储器六介绍多处理器和多线程技术,在计算机系统中一般划分为硬件和软件两个部分。

在硬件上,按照计算机规模,大到仓库规模,如超级计算机系统,小到智能手机系统,计算机包括中央处理器,存储器输入输出,其中高速缓存存储器cache是存储器的一种,中央处理器,包括执行单元功能单元cache功能单元。一般通过逻辑门构建在软件上,程序利用不同层次的并行与硬件系统适配,从而实现计算机系统的高效能,这里如图所示的定义主要包括任务级并行。

在多个计算机上并行执行线程级并行,在多个处理器合格并执行指令级并行,通过同一时刻发射多条指令,利用多个功能单元,同时执行发射多条指令数据级并行,同一时刻对不同的数据做相同的运算操作,同时可以通过。硬件描述语言来描述硬件逻辑单元的并行,这也是硬件语言的特点之一一般来说,与软件开发最相关的是数据级并行指令级并行线程级并行任务级并行。

计算机及结构设计的主要思路包括,一采用抽象方法来表示不同的层次,从而便于系统的设计与实现,二基于摩尔定律来预测处理器设计与工艺技术之间的关系,三采用局部性原理设计存储器层次结构四。采用并行性和阿姆达尔定律给出处理器系统的约束条件,五,通过荣誉模块设计实现系统的可靠性,我们整个课程会结合上述的五个思路来讲解我们的课程,我们看到计算机系统从高级语言到底层电路实现之间的。

抽象层次之间的关系示意图左图表示的是抽象层次,右图对应的是各个层次的描述,高级语言汇编代码,机器码结构电路的对应图,从左图我们可以看到,高级语言程序经过编译器被编译为汇编语言程序,汇编语言程序。由汇编器编译为对应的VS5的机器码,机器码与意念体结构描述有相对应的逻辑关系及结构的实现,对应与逻辑电路或电路原理图的设计,摩尔定律与摩尔骆氏是由英特尔创始人之一戈登摩尔提出的。

他预测,集中电路上可容纳的晶体管数目约每隔两年便会增加一倍,经常被赢的18个月是我英特尔首席执行官大卫豪斯提出的,预计18个月会将新的性能提高一倍及更多的晶体管,使其更快,是一种以倍数增长的观测摩尔定律,从目前来看一直有效从下图。我们可以看到密度也是考察特性之一,这个图来自于台积电TSMC在2019年后tips的专题演讲,采用局部性原理来设计处理器,存储器层次离处理器最近的这种单元分别是寄存器cache物理存储固态存储器虚拟存储器等。

这个存储器层次,我们在后面的讲解中会分别详细介绍适应性,如任务级并行指令级并行和线程级并行等,阿姆达尔定律,与阿姆的love是一个计算机科学界的经验法则,因吉恩阿姆达尔德里,它代表着处理器并行运算之后。效率提升的能力并行计算中的加速使用定型前的执行速度和定型后的执行速度之比来表示的,他表示了在定型化之后的效率提升情况,阿姆达尔定律是固定复杂的量化标准,该定理是指系统中某一部件采用更快执行方式所能。

进程度取决于这种执行方式被使用的频率或所占总执行时间的比例,我们可以通过荣誉模块设计实现可靠性荣誉取得失效的部分不会使整个系统失效,增加经济网密度可降低荣誉成本,我们可以看到,通过荣誉模块设计,实现可靠性的例子是用于从数据中心到存储器。到内存的所有设计中,例如通过数据中心的荣誉设计保证互联网络服务正常,谷歌公司提出的荣誉计算机的设计思路,独立磁盘冗余阵列的设计以及荣誉存储系统的设备设计等,如何在晶体结构的研究工作呢,我们从图中可以观察到。

目前,业界先进的cpu速度基本上维持在5G赫兹左右,但是经济管的提升度还在逐步提高,对设计功耗都有约束,而目前有很多应用需求,如云计算可视化虚拟现实增强现实娱乐自动驾驶教育医疗等应用。需求驱动各种架构的设计研究,因此需要应用编程创新和其架构的创新有机结合,才有可能提升系统性能体系架构,随着应用和工艺技术也在不断的引进应用需求驱动技术的改进,改进的技术使应用成为现实,可能耳机应用性的软件开发成为目前。

我们看到如下的信息应用对数据局部性原理的需求,这个图取自国际固态电路年会,STC,我们选取了嵌入式神经网络在人工智能方面的应用,如图中所示的人脸识别增强现实等应用,如果从边缘端传输数据到云端进行处理,会耗费较大的能量。和暴露用户隐私,因此目前一般建议在边缘端进行处理,要求的能力效率为1t ox,到时t ox没完,未来的应用需要不可估量的计算能力,如高性能计算机器智能大数据分析等应用。

高性能计算的应用,例如探索太空预测气候变化研制新药机器学习实时仿真等,这些应用对超级计算机提出了大算力的需求,2021年超级计算机可以达到每秒1500亿次浮点运算的能力,本讲我们介绍了计算机系统的表示,课程的主要内容及应用需求和体系架构,软件系统设计研究的必要性,本节课上到这里谢谢各位同学。

此处可能存在不合适展示的内容,页面不予展示。您可通过相关编辑功能自查并修改。

如您确认内容无涉及 不当用语 / 纯广告导流 / 暴力 / 低俗色情 / 侵权 / 盗版 / 虚假 / 无价值内容或违法国家有关法律法规的内容,可点击提交进行申诉,我们将尽快为您处理。

13:R型指令和I型算术指令视频

These slides contain material from courses: USB CS61C.

【读书笔记】《Computer Organization and Design: The Hardware/Software Interface》(1)

https://blog.csdn.net/weixin_30256505/article/details/99564193

weixin_30256505 2018-12-19 10:35:00

转载于:https://www.cnblogs.com/luhuidu/p/10141749.html

相关资源:Computer Organization and Design The Hardware Software Interface ARM 无水印pdf

Computer Organization and Design The Hardware Software interface 阅读笔记3

https://blog.csdn.net/qq_26371477/article/details/109705452

源级小赵 2020-11-18 09:13:42 阅读笔记 1 2 4 5

《计算机组成与设计》David A.Patterson-英文原版之处理器4.1,4.2章节思维导图(一) (二) (三)

21:控制冒险以及超标量处理器

lw Data Hazard

22:存储器层次结构

图书馆为例!

高速缓存(Cache)

局部性原理

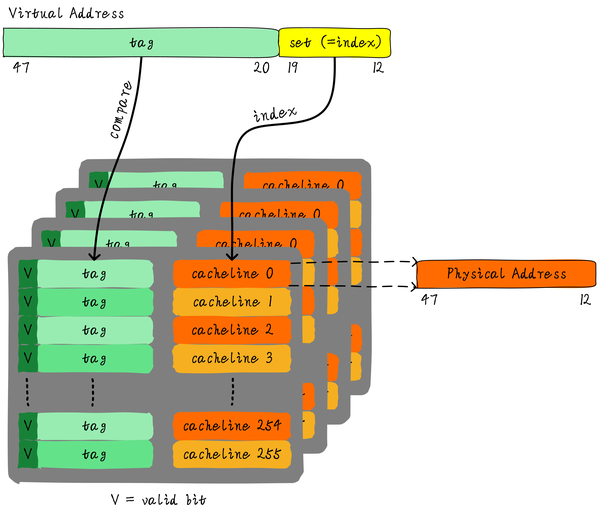

Cache Design

Recap

RV4Kids/Shiliu PI, Shiliu Silicon, Shiliu Si, 石榴核.md

收录!

将被 PLCT 实验室 汪辰老师的“从0”计算机操作系统课替代,并以石榴派为实验系统。

这是第一份 RV4kids 的学习笔记,详实完整,对整个计算机体系结构有了全面的了解。

登录 后才可以发表评论