代码拉取完成,页面将自动刷新

Σ-Δ ADC一眼看上去,都看不出能AD转换,给人一种“这真的是ADC吗”的感觉。

本人才疏学浅,大神讲解得更深入:B站链接

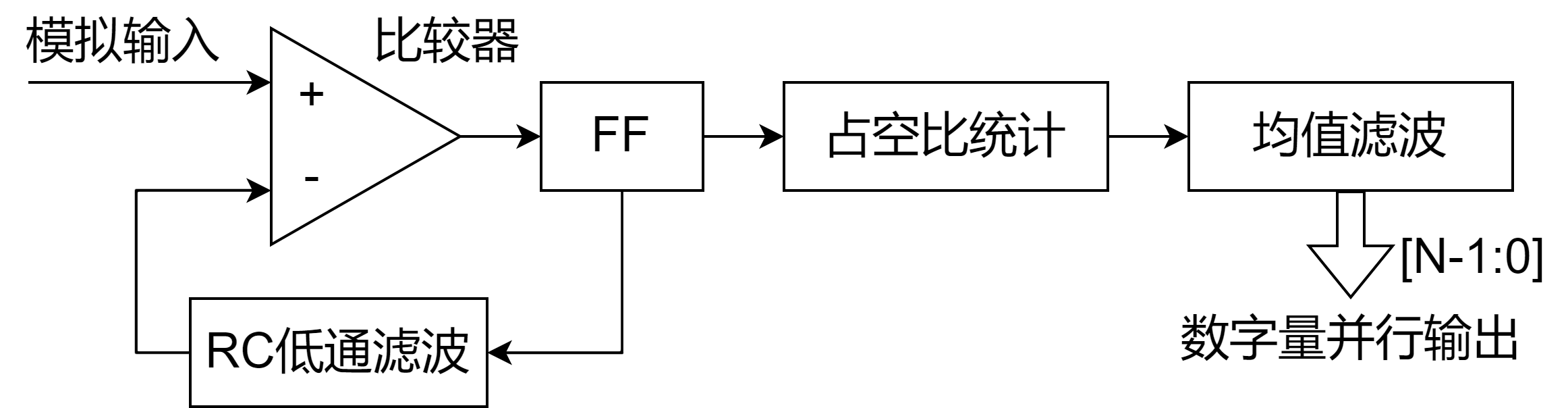

显而易见,这是一个比较器,或者是一个工作在比较器状态的运放。

模拟信号连接至正相输入端,反馈信号经过RC滤波连接至反相输入端,比较器输出连接至FPGA。

RC滤波器是一个低通滤波器,截止频率与ADC的采样速率和FPGA工作频率有关。

外围电路将模拟信号转换为1位的01序列,这样我们就能用数字逻辑去处理模拟信号。

windows环境,需要安装iverilog。

clone项目,进入RTL/tb,运行make.bat

k7_fpga.rar是vivado 2019.2的工程,配合硬件电路/提供的原理图,可以实现Σ-Δ ADC。

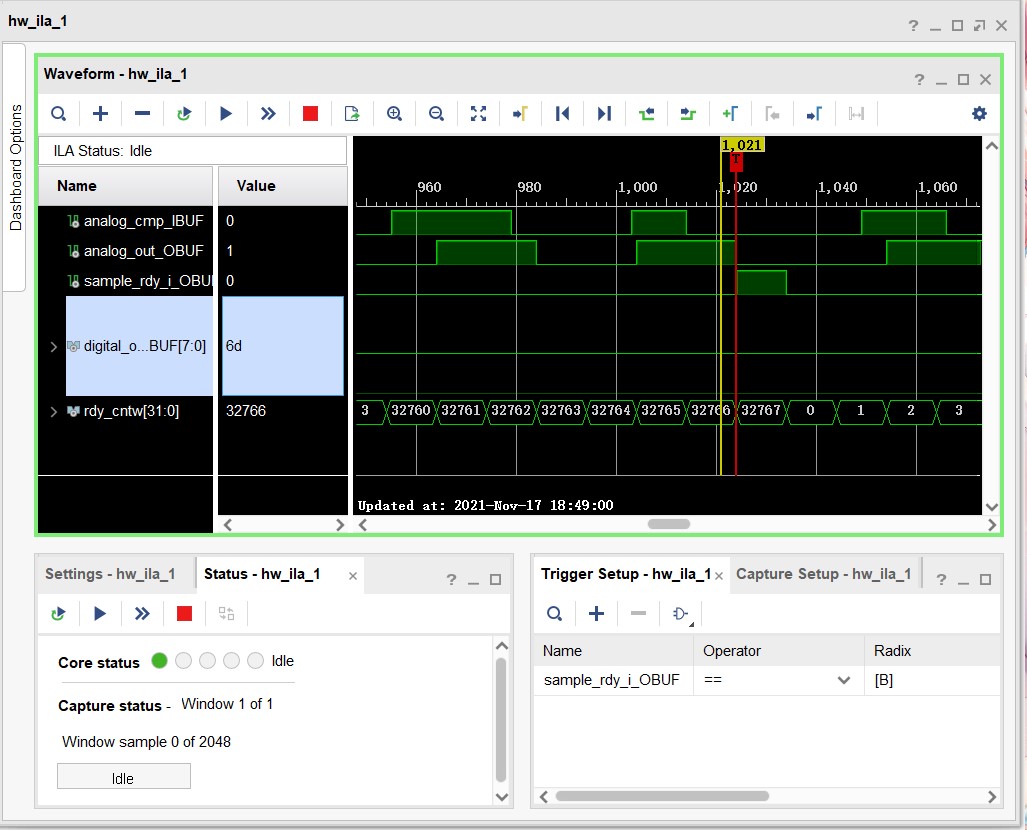

使用7k325连接外围电路,采集电压,8bit输出。内置逻辑分析仪查看情况。

sample_rdy高电平脉冲表示一次转换结束,输出结果为0x6d。

实验的ADC位宽为8bit,量程是0-3.3V,那么实际电压为0x6d/0xff*3.3=1.41v,与万用表测量结果吻合。

此处可能存在不合适展示的内容,页面不予展示。您可通过相关编辑功能自查并修改。

如您确认内容无涉及 不当用语 / 纯广告导流 / 暴力 / 低俗色情 / 侵权 / 盗版 / 虚假 / 无价值内容或违法国家有关法律法规的内容,可点击提交进行申诉,我们将尽快为您处理。